Intel demonstrated the first multi-chiplet package using Universal Chiplet Interconnect Express (UCIe) interconnects.

Universal Chiplet Interconnect Express (UCIe) is an open industry standard for a die-to-die interconnect and serial bus between chiplets. It is co-developed by AMD, Arm, ASE Group, Google Cloud, Intel, Meta, Microsoft, Qualcomm, Samsung, and TSMC. In August 2022, Alibaba Group and Nvidia joined as board members. The open specification is now supported by more than 120 companies.

Intel's test chip combined an Intel UCIe IP chiplet fabricated on Intel 3 and a Synopsys UCIe IP chiplet fabricated on TSMC N3E process node. The chiplets are connected using embedded multi-die interconnect bridge (EMIB) advanced packaging technology. The demonstration highlights the commitment of TSMC, Synopsys and Intel Foundry Services to support an open standard-based chiplet ecosystem with UCIe.

Additional highlights of the first day of Intel Innovation 2023 event in San Jose

- Intel confirmed its five-nodes-in-four-years process technology plan remains on track. Intel 7 already in high-volume manufacturing, Intel 4 manufacturing-ready and Intel 3 on track for the end of this year. An Intel 20A wafer was displayed showing the first test chips for Intel’s Arrow Lake processor, which is destined for the client computing market in 2024. Intel 20A will be the first process node to include PowerVia, Intel’s backside power delivery technology, and the new gate-all-around transistor design called RibbonFET. Intel 18A, which also leverages PowerVia and RibbonFET, remains on track to be manufacturing-ready in the second half of 2024.

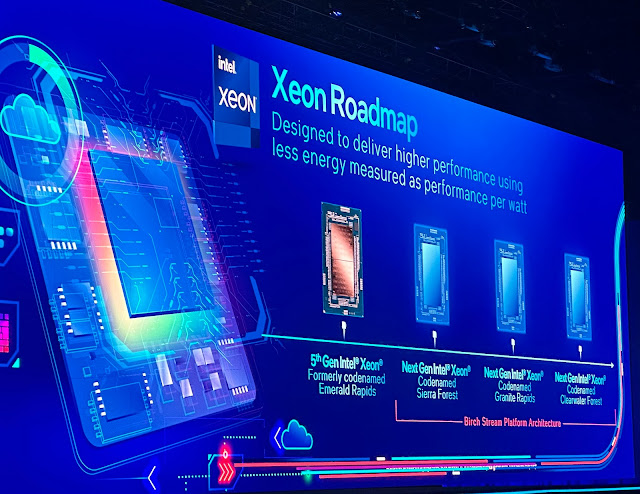

- The company revealed new details on next-generation Intel Xeon processors, including major advances in power efficiency and performance, and an E-core processor with 288 cores. 5th Gen Intel Xeon processors will launch Dec. 14. Sierra Forest, with E-core efficiency and arriving in the first half of 2024, will deliver 2.5x better rack density and 2.4x higher performance per watt over 4th Gen Xeon and will include a version with 288 cores2. And Granite Rapids, with P-core performance, will closely follow the launch of Sierra Forest, offering 2x to 3x better AI performance compared to 4th Gen Xeon. Looking ahead to 2025, the next-gen E-core Xeon, code-named Clearwater Forest, will arrive on the Intel 18A process node.

- The AI PC arrives with the launch of Intel Core Ultra processors on Dec. 14. With Intel’s first integrated neural processing unit, Core Ultra will deliver power-efficient AI acceleration and local inference on the PC.

- A large AI supercomputer will be built on Intel Xeon processors and Intel® Gaudi 2 AI hardware accelerators, with Stability AI as the anchor customer.

“AI represents a generational shift, giving rise to a new era of global expansion where computing is even more foundational to a better future for all,” said Intel CEO Pat Gelsinger. “For developers, this creates massive societal and business opportunities to push the boundaries of what’s possible, to create solutions to the world’s biggest challenges and to improve the life of every person on the planet.”