The Open Compute Project Foundation (OCP) released of a new chiplet interconnect link layer specification and an evolution of its previously-released Bunch of Wires (BoW) PHY specification.

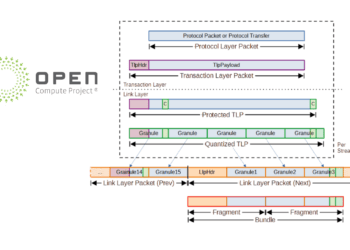

- The development of the OCP ODSA (Open Domain-Specific Architecture) Link Layer specification is focused on the silicon die disaggregation use case maintaining simplicity to serve as many markets as possible, with key features, such as: (1) extensibility defining interface profiles allowing the addition of new link layer features, customization to bus protocols and enabling Chiplet interconnect interoperability, (2) portability across different die implementation methodologies and process nodes, (3) ability to scale with support for multiple PHY slices and different data rates, (4) while keeping latency low, especially with use of Forward Error Correction (FEC) eliminating where possible serialization due to Cyclic Redundancy Check (CRC).

- BoW 2.0 includes significant advancements on top of doubling top speed to 512 Gbps per 16 lane slice, including: (1) new energy efficient operations with gated clock and data line inactive modes that can save up to 90% of power consumed for interconnect, (2) half-width slices for dies with smaller absolute beachfront requirements, (3) sideband slices for channel management, (4) bidirectional slices with direction configurable across channel, and (5) and bump redundancy for improved reliability on failure.

“We can see the first visible seedlings of the open Chiplet economy sprout with the release of LL 1.0 and BoW 2.0 complementing the recent release of CDXML and establishing an alliance with JEDEC and work on standardized Chiplet test benches and interconnect benchmarks. We are at an inflection point where Chiplet vendors have a fairly complete set of standards and tools available to derisk building Chiplet product sets. The market leaders developing Chiplets are still playing a very important role filling gaps that they identify in current standards and we expect to see these additional learnings materialize as updates to existing standards as the open Chiplet economy matures,” said Bapi Vinnakota Ph.D., ODSA Project lead at OCP.

https://www.opencompute.org/blog/open-compute-project-pushes-fast-forward-on-an-open-chiplet-economy